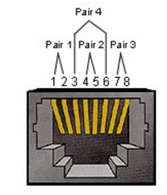

1RJ45插头、插座RJ45接口定义以及各引脚功能在不同通信速率下的定义有区别,12是在10M/100M通信速率下的定义,由下可知,RJ45插座只使用了6这四根线,其中2这组负责传输数据,而6这组负责接收数据,另外四根线是备用的。

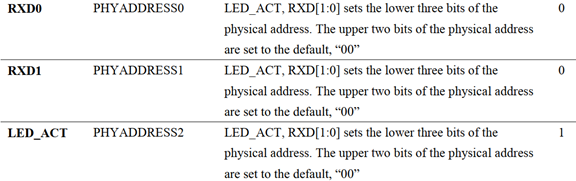

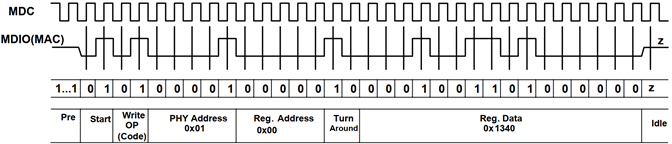

MDIO接口写时序上是以PHY地址为0x0向寄存器地址0x00写入0x1340为例,在整个写操作过程中,MDC时钟和MDIO引脚一直由MAC端驱动,按照MDIO接口写通信协议开始传输数据。需要注意的是,PHY在MDC时钟的上升沿采集数据,为保证数据的稳定传输,MAC在MDC的下降沿将数据更新至MDIO引脚。在写操作结束后,MAC将MDIO引脚输出高阻,此时MDIO引脚的外部上拉电阻会将MDIO引脚拉高,此时MDIO接口处于空闲状态。以太网PHY芯片PHY地址YT8511芯片的PHY地址由LED_ACT和RXD[1:0]引脚决定,如下所示:PHY地址一共有五位,其中高两位固定为00,LED_ACT和RXD[1:0]引脚表示低三位,我们可以通过硬件电路设置LED_ACT和RXD[1:0]引脚引脚为上拉或者下来,即分配为高低电平,0或从而表示不同的地址。

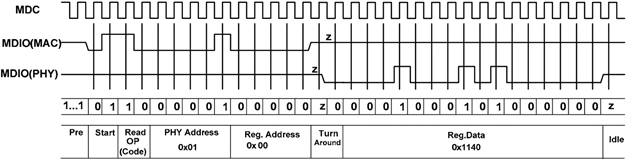

MDIO接口读时序上是以PHY地址为0x0从寄存器地址0x00读出数据为例。整个读操作过程的MDC时钟由MAC驱动,同时MAC驱动MDIO引脚输出前导码+帧开始+操作码+PHY地址+寄存器地址,随后MDIO引脚切换至PHY驱动。在第一个TA位,MDIO引脚为高阻状态,第二个TA位为低电平,表示PHY芯片成功响应,并且接下来会输出16位寄存器数据;而如果第二个TA位处于高电平,则PHY芯片响应失败,有可能PHY地址不正确或者其它时序的错误。需要注意的是,PHY在MDC时钟的上升沿采集数据,为保证数据的稳定传输,MAC在MDC的下降沿更新MDIO引脚的数据。当MDIO引脚切换至PHY驱动时,MDIO数据在MDC时钟的下降沿更新,因此MAC在MDC时钟的上升沿采集数据。在读操作结束后,MAC将MDIO引脚输出高阻,此时MDIO引脚的外部上拉电阻会将MDIO引脚拉高,此时MDIO接口处于空闲状态。MDIO接口写时序如下所示:

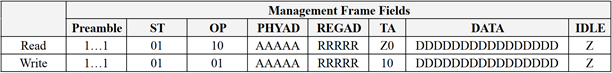

MDIO接口通信协议Preamble:32位前导码,由MAC端发送32位逻辑“1”,用于同步PHY芯片。ST:2位帧开始信号,用01表示。OP:2位操作码,读:10写:0PHYAD:5位PHY地址,用于表示与哪个PHY芯片通信,因此一个MAC上可以连接多个PHY芯片。REGAD:5位寄存器地址,可以表示共32位寄存器。TA:2位转向,在读命令中,MDIO在此时由MAC驱动改为PHY驱动,在第一个TA位,MDIO引脚为高阻状态,第二个TA位,PHY将MDIO引脚拉低,准备发送数据;在写命令中,不需要MDIO方向发生变化,MAC固定输出2’b10,随后开始写入数据。DATA:16位数据,在读命令中,PHY芯片将读到的对应PHYAD的REGAD寄存器的数据写到DATA中;在写命令中,PHY芯片将接收到的DATA写入REGAD寄存器中。需要注意的是,在DATA传输的过程中,高位在前,低位在后。IDLE:空闲状态,此时MDIO为无源驱动,处于高阻状态,但一般用上拉电阻使其上拉至高电平。MDIO接口读时序如下所示:

在以太网通信中,设备之间的物理层链路均由PHY芯片建立。PHY芯片有一个配置接口,即MDIO接口,可以配置PHY芯片的工作模式以及获取PHY芯片的若干状态信息。本章我们来学习如何通过领航者ZYNQ开发板实现对PHY芯片的MDIO接口进行读写测试。本章分为以下几个章节:1简介2实验任务3硬件设计4程序设计5下载验证 1简介以太网概述以太网(Ethernet)是当今现有局域网采用的最通用的通信协议标准,该标准定义了在局域网中采用的电缆类型和信号处理方法。以太网凭借其成本低、通信速率高、抗干扰性强等优点被广泛应用在网络远程监控、交换机、工业自动化等对通信速率要求较高的场合。以太网是一种产生较早,使用相当广泛的局域网。其最初是由Xerox公司创建并由Xerox、Intel和DEC公司联合开发的基带局域网规范,后来被电气与电子工程师协会所采纳作为803的标准。以太网的分类有标准以太网,快速以太网(100Mbit/s)和千兆以太网。随着以太网技术的飞速发展,市场上也出现了万兆以太网,它扩展了IEEE803协议和MAC规范,使其技术支持10Gbit/s的传输速率。在实际应用中,千兆以太网理论上最高通信速率为1000Mbit/s,可以胜任大部分的使用场景。以太网通信离不开连接端口的支持,网络数据连接的端口就是以太网接口。以太网接口类型有RJ45接口,RJ11接口,SC光纤接口等。其中RJ45接口是我们现在最常见的网络设备接口,我们开发板使用的就是这种接口。RJ45接口俗称“水晶头”,专业术语为RJ45连接器,由插头和插座组成,属于双绞线以太网接口类型。RJ45插头只能沿固定方向插入,设有一个塑料弹片与RJ45插槽卡住以防止脱落。RJ45接口样式如11所示:

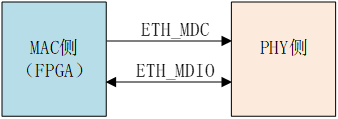

MDIO接口示意MDIO接口也称为SMI接口,包括ETH_MDC和ETH_MDIO两条信号线。ETH_MDC为ETH_MDIO提供时钟,ETH_MDC的最大时钟不能超过15Mhz。ETH_MDIO为双向数据引脚,既用于发送数据,也用于接收数据。MDIO接口的读写通信协议如下所示:

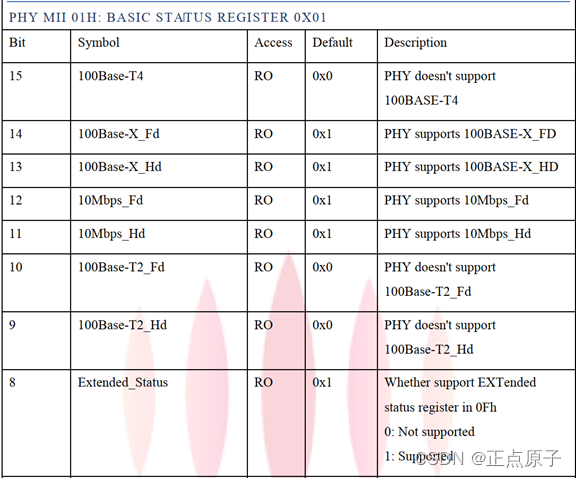

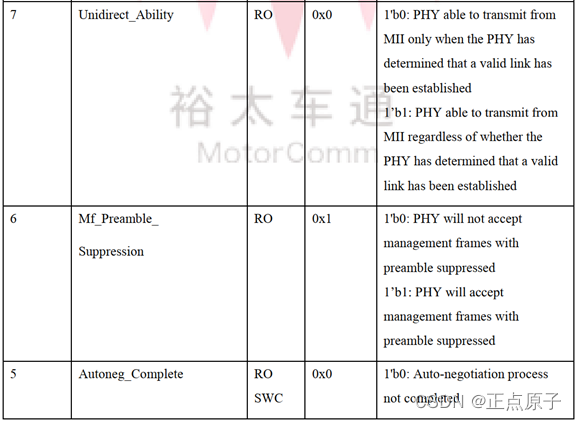

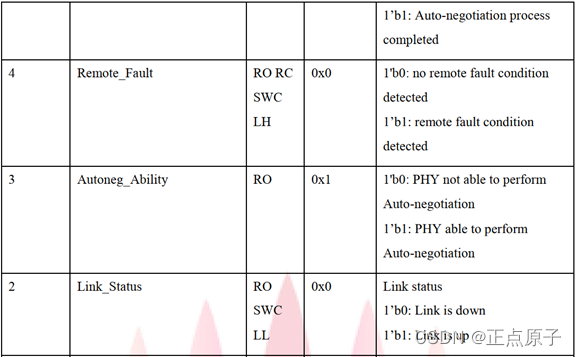

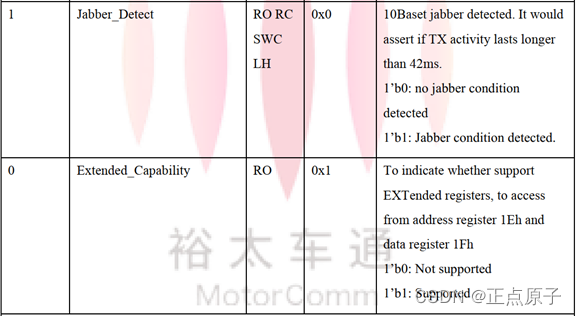

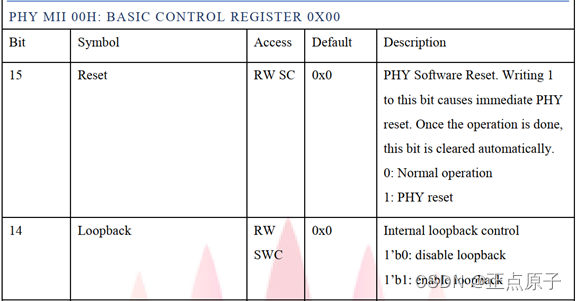

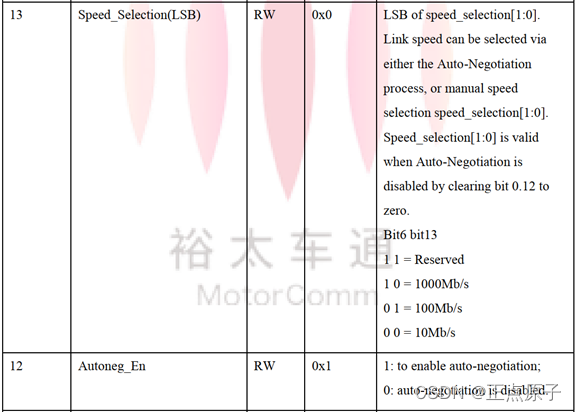

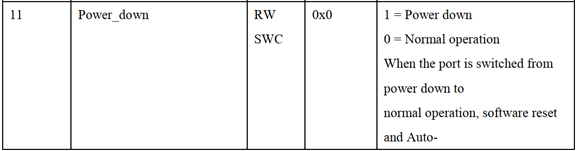

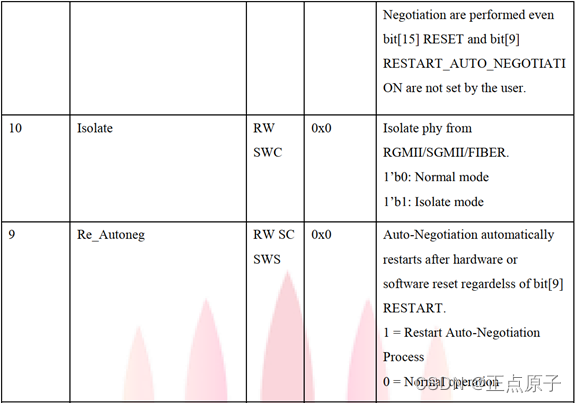

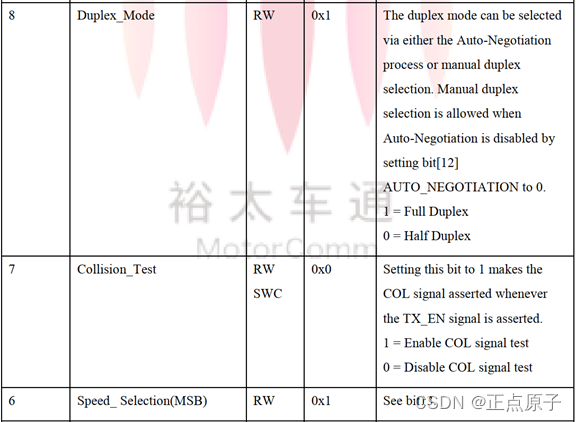

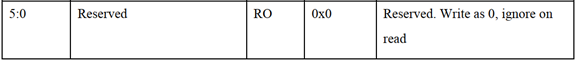

控制寄存器说明部分常用位的说明如下:Bit[15]:软件复位,PHY复位0:正常模式;Bit[14]:内部环回模式,内部环回模式0:正常模式;BitBit[13]:选择网速带宽只有在自动协商使能不开启的情况下有效,10:1000Mb/s0100Mb/s00:10Mb/s;Bit[12]:自动协商使能自动协商使能0:自动协商不使能;Bit:重启自协商,重新开始自协商0:自协商重启完成。基本状态寄存器(BasicModeStatusRegister,Address0x0,简写为:BMSR,各个位的说明如下所示:

PHY地址选择LED_ACT和RXD[1:0]取不同的值表示的地址范围从00001到0011领航者开发板上的以太网PHY芯片LED_ACT接上拉电阻,RXD[1:0]接下拉电阻,因此PHY地址为5’b00100。复位YT8511芯片复位后,PHY内部寄存器的数据会恢复默认的状态,并且重新开始和MAC进行自协商。YT8511支持两种复位方式,一种是硬件复位,另外一种是软件复位。硬件复位时通过ETH_RST_N引脚实现对PHY芯片的复位,当ETH_RST_N引脚持续10ms的低电平时,即可实现对PHY芯片的复位。软件复位通过向寄存器地址0x00的Bit[15]写入1进行复位,并且在完成复位后,该位会自动清零。寄存器YT8511共有22位寄存器,这里我们仅介绍本实验用到的三个寄存器,控制寄存器、状态寄存器以及PHY芯片具体状态寄存器。控制寄存器(BasicModeControlRegister,Address0x00),简写为:BMCR,用于芯片的复位和其它功能的控制,各个位的说明如下所示:

RJ45插座10M/100M接口定义而在1000M的通信速率下,RJ45插座的8根线都有用到,且都是双向引脚。需要说明的是,支持千兆网通信的RJ45接口是向下兼容的,即也支持10M/100M通信速率,只不过不同的通信速率,其引脚功能有区别。千兆网各引脚功能如下所示:

RJ45插座1000M接口定义从硬件的角度来说,以太网接口电路主要由MAC控制器和物理层接口PHY两大部分构成。MAC指媒体访问控制子层协议,它和PHY接口既可以整合到单颗芯片内,也可以独立分开,对于本次设计来说,MAC控制器由FPGA实现,PHY芯片指开发板板载的以太网芯片。PHY在发送数据的时候,接收MAC发过来的数据,把并行数据转化为串行流数据,按照物理层的编码规则把数据编码转换为模拟信号发送出去,接收数据时的流程反之。PHY还提供了和对端设备连接的重要功能,并通过LED灯显示出自己目前的连接状态和工作状态。当我们给网卡接入网线的时候,PHY芯片不断发出脉冲信号来检测对端是否有设备,它们通过标准的“语言”交流,互相协商并确定连接速度、双工模式、是否采用流控等。通常情况下,协商的结果是两个设备中能同时支持的最大速度和最好的双工模式。这个技术被称为AutoNegotiation,即自协商。MDIO接口MAC和PHY芯片有一个配置接口,即MDIO接口,可以配置PHY芯片的工作模式以及获取PHY芯片的若干状态信息。PHY芯片内部包含一系列寄存器,用户通过这些寄存器来配置PHY芯片的工作模式以及获取PHY芯片的若干状态信息,如连接速率、双工模式、自协商状态等。FPGA通过MDIO接口对PHY芯片内部的寄存器进行配置。通常情况下,PHY芯片在默认状态下也可以正常工作,在做以太网通信实验时,对MDIO接口的配置不是必须的,本章旨在向大家介绍MDIO接口以及如何对MDIO接口进行读写操作。MAC和PHY连接示意如下所示。

11特定状态寄存器Bit[15:14]:连接速度1保留10:1000Mbps0100Mbps00:10Mbps2实验任务本节实验任务是使用领航者ZYNQ开发板上的以太网接口,完成MDIO接口的读写测试实验。板载的触摸按键控制MDIO接口进行软复位,并通过两个LED灯实时指示当前网口的连接速度。

文章为作者独立观点,不代表股票交易接口观点