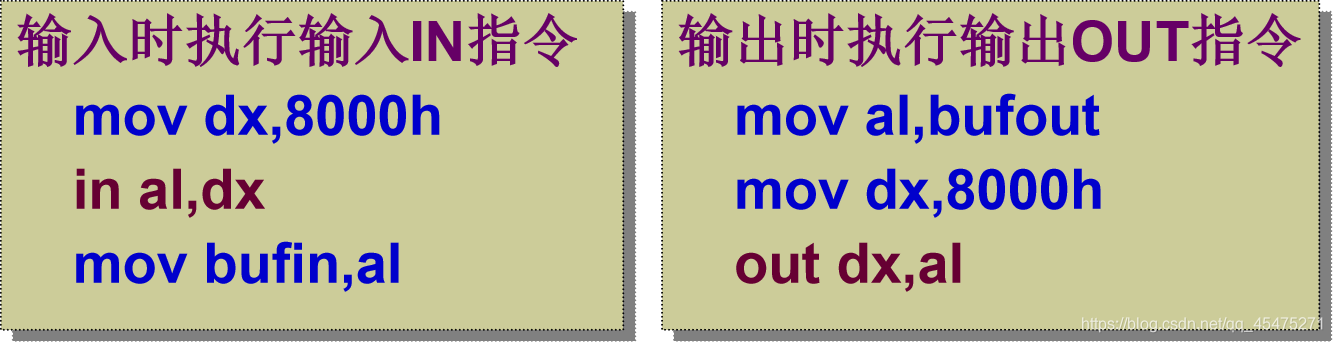

输入指令IN:数据从I/O通达信c+通达信c+接口,接口,通达信c+接口,接口输入到微处理器

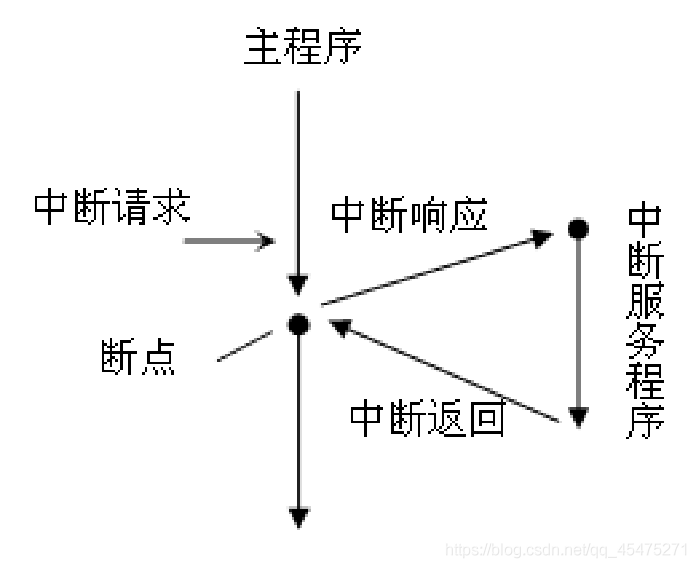

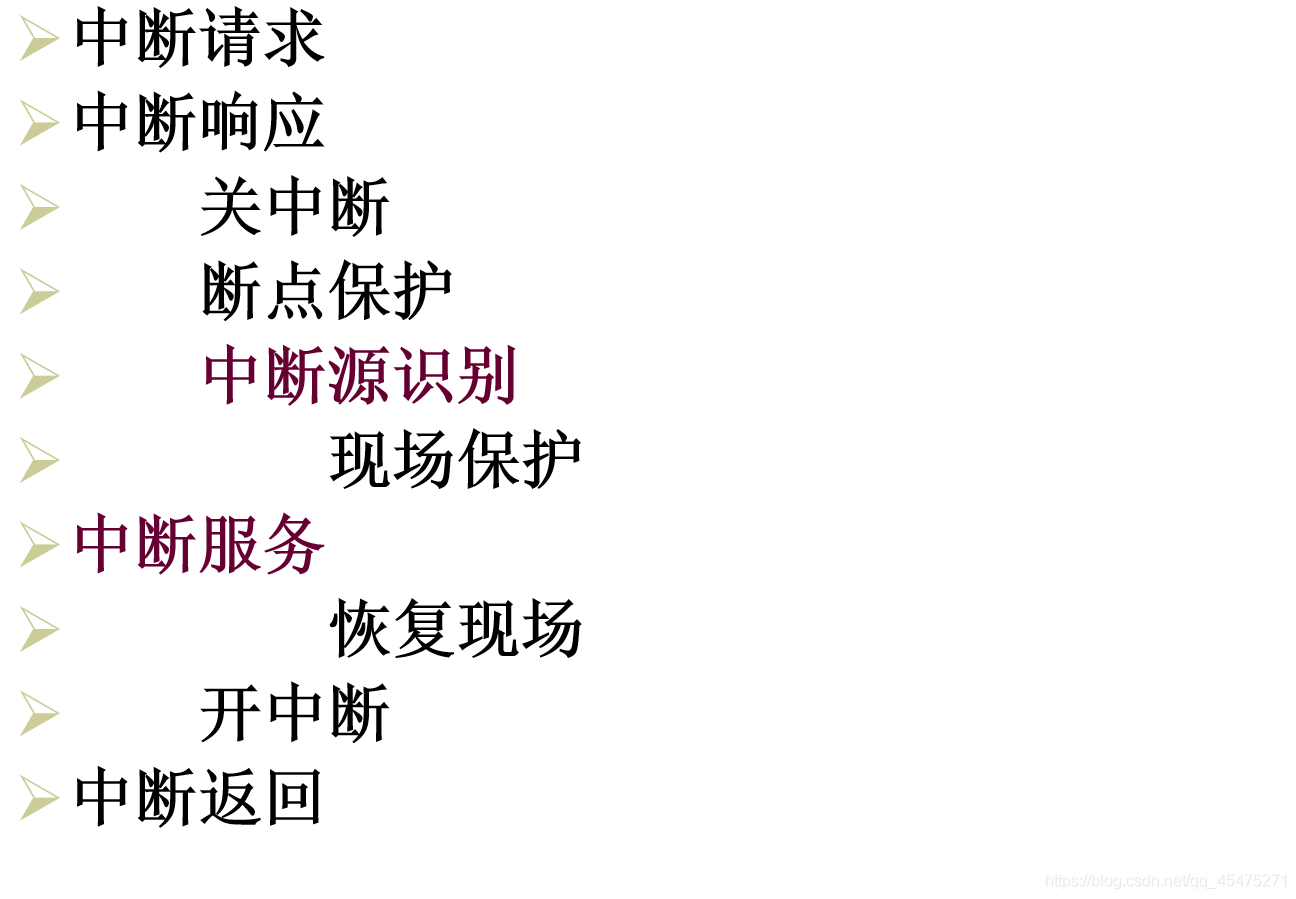

·处理器在执行程序过程中,被内部或外部的事件所打断,转去执行一段预先安排好的中断服务程序;服务结束后,又返回原来的断点,继续执行原来的程序·中断源:引起中断的事件或原因·内部中断·外部中断:可屏蔽中断、非屏蔽中断

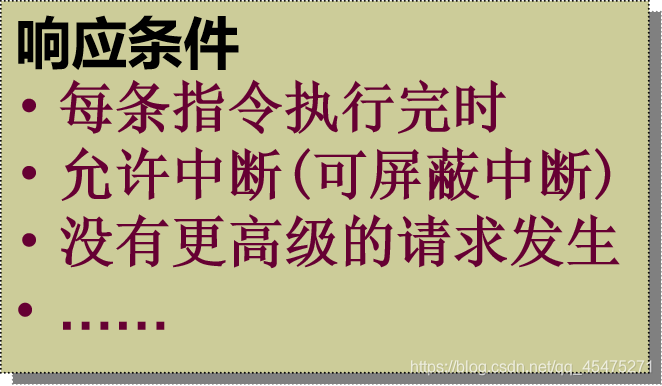

外部中断·非屏蔽中断外部通过非屏蔽中断NMI请求信号提出的中断处理器在当前指令执行结束予以响应非屏蔽中断的中断向量号是2非屏蔽中断主要用于处理系统的意外或故障·可屏蔽中断外部通过可屏蔽中断INTR请求信号提出的中断允许可屏蔽中断的条件下、当前指令执行结束予以响应输出可屏蔽中断响应信号INTA*,产生可屏蔽中断响应总线周期,读取中断向量号需要中断控制器负责处理中断优先权排队等管理工作可屏蔽中断主要用于与外设进行数据交换

除法错异常执行除法指令时,若除数为0或商超过了寄存器所能表达的范围,产生的一个向量号为0的内部中断

; 数据段

msg byte 0dh,0ah, 'No pide overflow !',0

; 代码段

call readuiw

mov bl,1

p bl

mov eax,offset msg ; 没有除法错,显示信息

call dispmsg

259A的寄存器·中断请求寄存器IRR保存8条外界中断请求信号IR0~IR7的请求状态Di位为1表示IRi引脚有中断请求·中断服务寄存器ISR保存正在被8259A服务的中断状态Di位为1表示IRi中断正在服务中·中断屏蔽寄存器IMR保存对中断请求信号IR的屏蔽状态Di位为1表示IRi中断被屏蔽

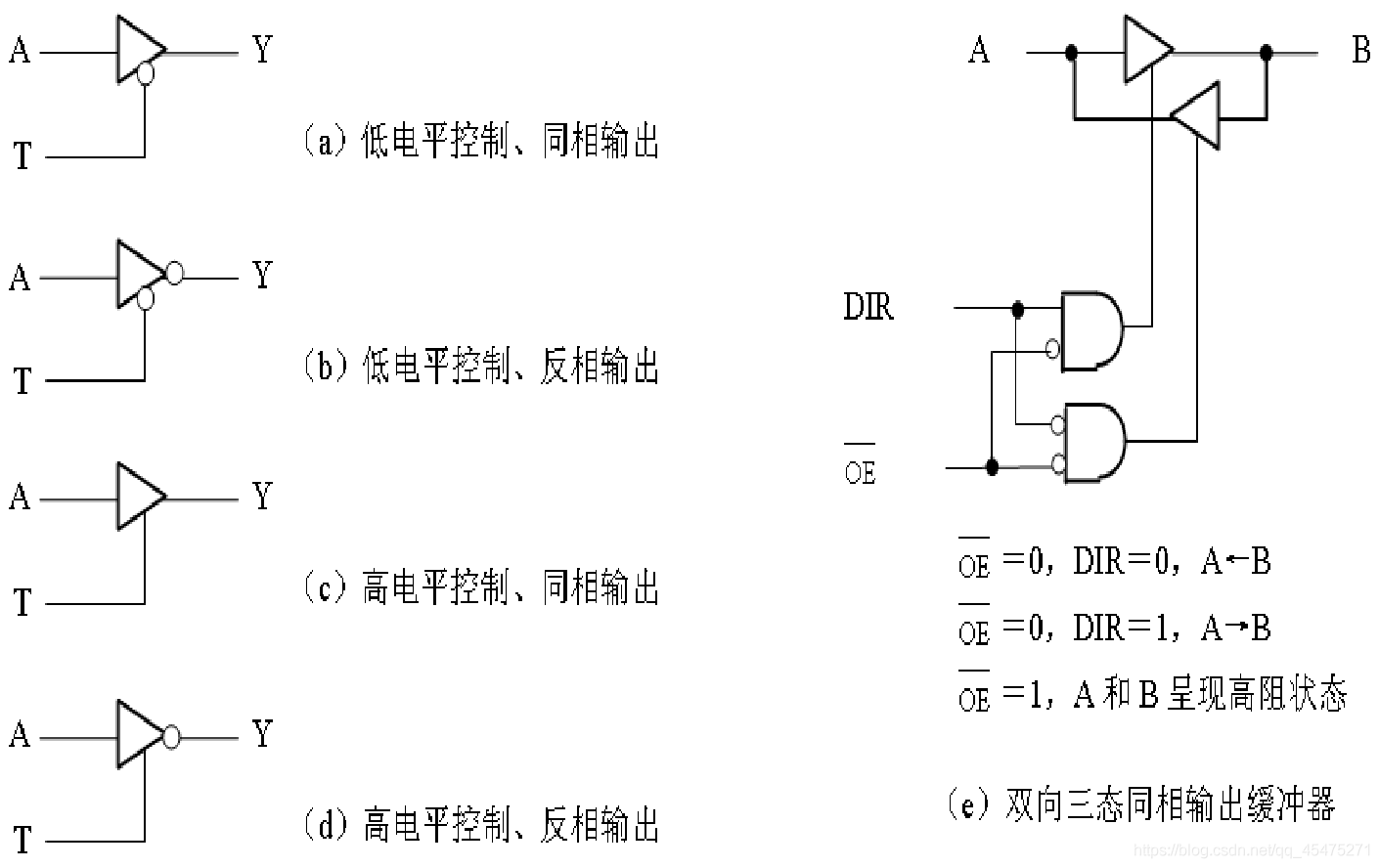

三态缓冲器·三态缓冲器:加有控制端的同相器或反相器控制端T有效时,控制输入A端输出到Y端控制端T无效时,输出Y端呈现高阻状态·74LS24双4位三态同相缓冲器·双向三态缓冲器:两个三态缓冲器构成输出允许控制端OE*:控制数据的输出方向控制端DIR:控制数据驱动的方向·74LS248位双向三态缓冲器芯片

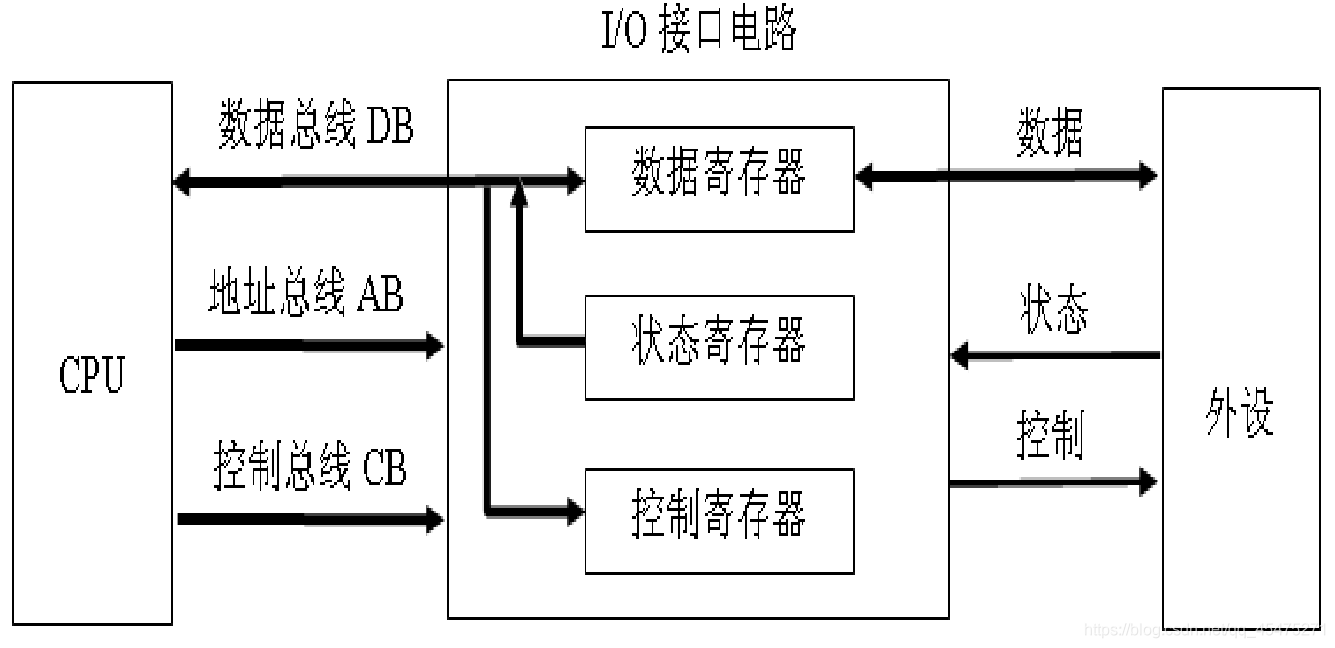

·微机的外部设备多种多样工作原理、驱动方式、信息格式、以及工作速度方面彼此差别很大它们不能与CPU直接相连必须经过中间电路再与系统相连·I/O通达信c+通达信c+接口,接口,通达信c+接口,接口是位于基本系统与外设间、实现两者数据交换的控制电路

I/O地址=外设端口,对应通达信c+通达信c+接口,接口,通达信c+接口,接口寄存器内部结构·数据寄存器保存处理器与外设之间交换的数据数据输入寄存器:保存从输入设备获取的数据,处理器选择合适的方式进行读取数据输出寄存器:保存处理器发往输出设备的数据,适时到达输出设备·状态寄存器保存通达信c+通达信c+接口,接口,通达信c+接口,接口电路和外设当前的工作状态信息·控制寄存器保存处理器控制通达信c+通达信c+接口,接口,通达信c+接口,接口电路和外设操作的有关信息外部特性·通达信c+通达信c+接口,接口,通达信c+接口,接口电路的外部特性由其引出信号来体现·I/O通达信c+通达信c+接口,接口,通达信c+接口,接口处于处理器与外设之间·面向微处理器一侧的信号:与处理器总线或系统总线类似,有数据信号、地址信号和控制信号等·面向外设一侧的信号:与外设有关,外设数据信号、外设状态信号和外设控制信号基本功能·数据缓冲匹配快速的处理器与相对慢速的外设的数据交换缓冲Buffer:实现通达信c+通达信c+接口,接口,通达信c+接口,接口双方数据传输的速度匹配·信号变换把信号相互转换为适合对方的形式计算机直接处理的信号:数字量;开关量;脉冲量软件编程·通达信c+通达信c+接口,接口,通达信c+接口,接口芯片具有可编程性·命令字写入通达信c+通达信c+接口,接口,通达信c+接口,接口芯片、选择工作方式、控制数据传输·初始化程序选择I/O通达信c+通达信c+接口,接口,通达信c+接口,接口工作方式、设置原始工作状态等·驱动程序操纵I/O通达信c+通达信c+接口,接口,通达信c+接口,接口完成具体工作

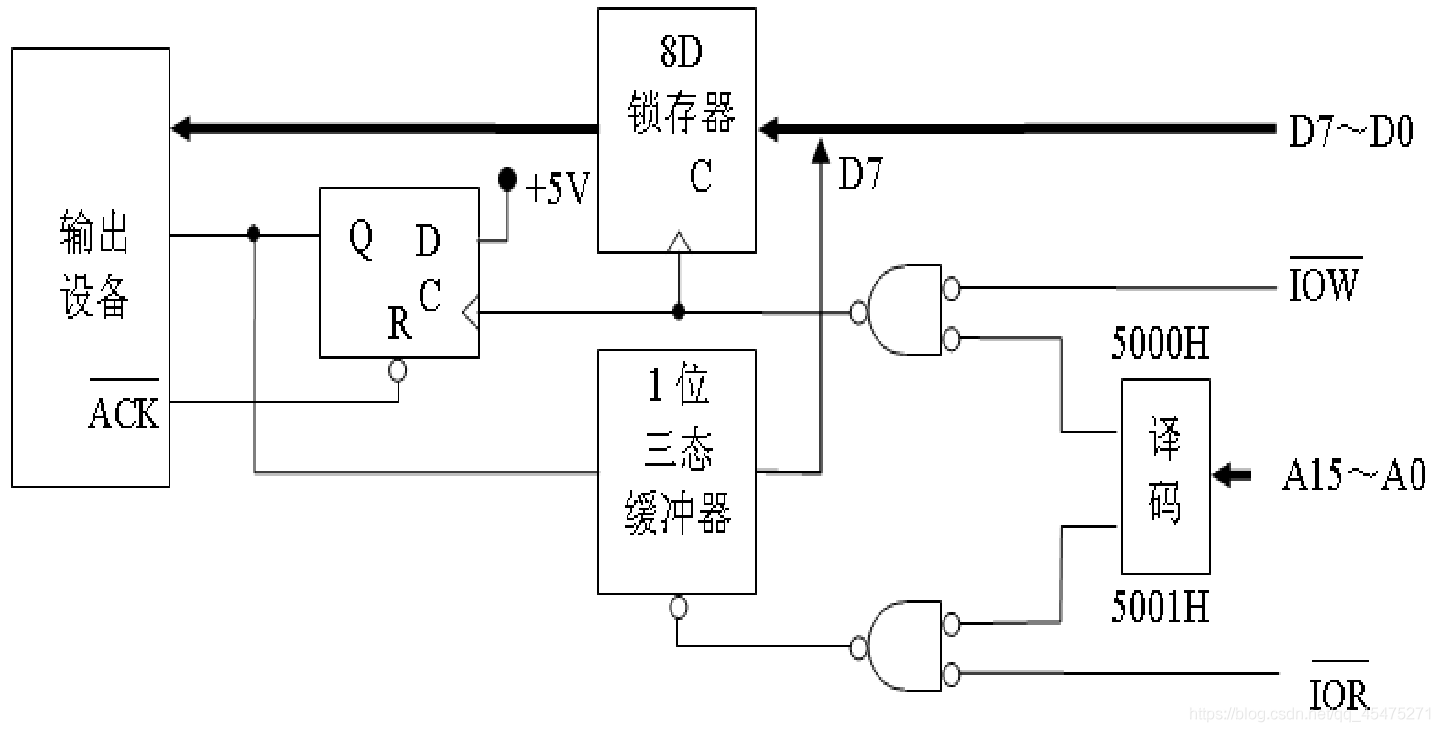

查询输入通达信c+通达信c+接口,接口,通达信c+接口,接口查询输出通达信c+通达信c+接口,接口,通达信c+接口,接口读取状态端口查询外设状态,若已就绪,将数据写入数据端口输出给外设

mov dx,5001h ;DX指向状态口

status: in al,dx ;读取状态口的状态数据

test al,80h ;测试标志位D7

jnz status ;D7=1,未就绪,继续查询

dec dx ;D7=0,就绪,DX改指数据口

mov al,buf ;将变量BUF送AL

out dx,al ;将AL中的数据送数据口

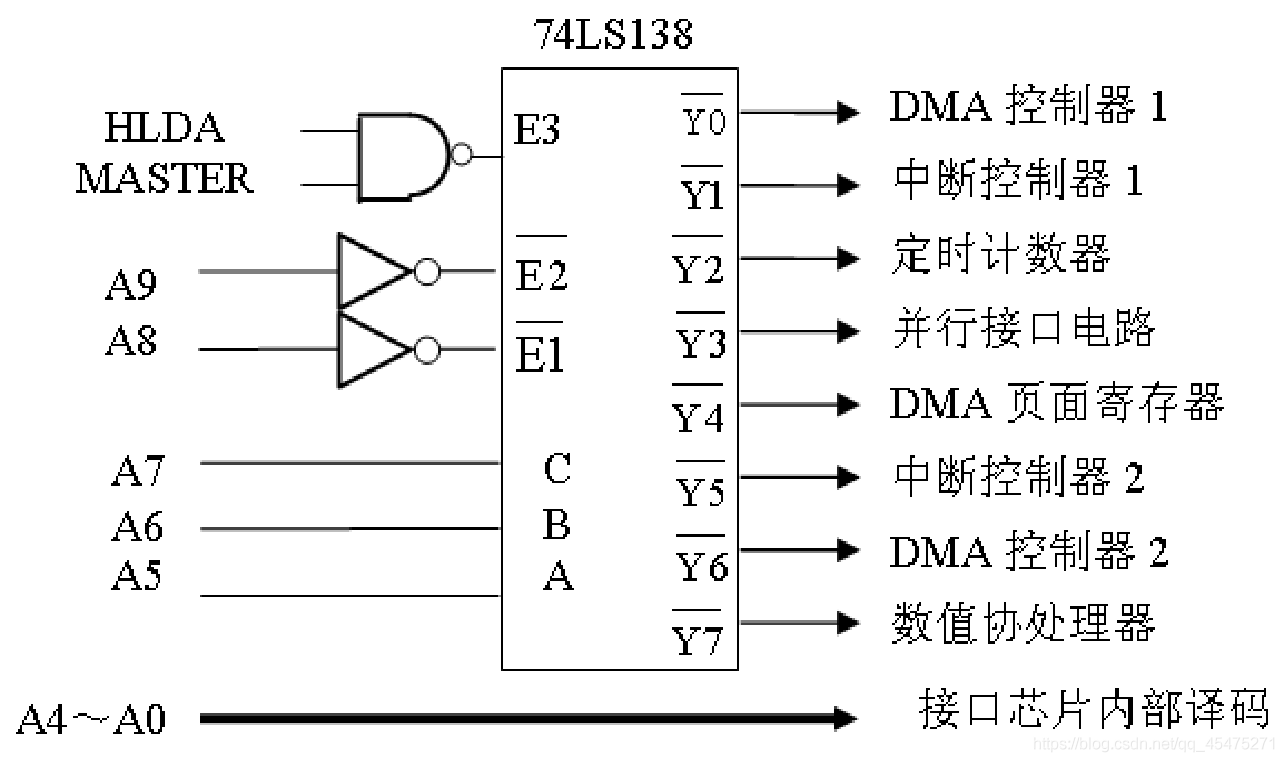

中断控制器

I/O端口=I/O地址,对应I/O通达信c+通达信c+接口,接口,通达信c+接口,接口的寄存器一个通达信c+通达信c+接口,接口,通达信c+接口,接口电路可以具有多个I/O端口,每个端口用来保存和交换不同的信息数据寄存器、状态寄存器和控制寄存器占有的I/O地址常依次被称为数据端口、状态端口和控制端口输入、输出端口可以是同一个I/O地址

输出指令OUT:数据从微处理器输出I/O通达信c+通达信c+接口,接口,通达信c+接口,接口

IA-32中断系统

溢出异常执行溢出中断指令INTO时,若溢出标志OF为产生的一个向量号4的内部中断

; 数据段

msg byte 0dh,0ah,'No overflow !',0

; 代码段

call readuib

add al,100

jno noflow ; 没有溢出,转移

into ; 有溢出,产生溢出中断

jmp done

noflow: mov eax,offset msg ; 显示无溢出信息

call dispmsg

done:

I/O寻址方式·直接寻址I/O指令直接提供8位I/O地址,只能寻址最低256个I/O地址。用i8表示I/O地址,表达形式上与立即数一样·DX间接寻址用DX寄存器保存访问的I/O地址,可寻址全部I/O地址。直接书写成DX,表示I/O地址I/O数据传输量8位I/O传输:I/O指令使用AL16位I/O传输:I/O指令使用AX32位I/O传输:I/O指令使用EAXI/O保护·I/O敏感指令:IN、OUT和INS、OUTS,CLI和STI·IA-32处理器保护方式下,I/O特权和I/O许可位限制I/O敏感指令的执行程序的当前特权高于或等于程序的I/O特权,I/O敏感指令才可以执行I/O许可位给特权低的程序或虚拟8086方式的程序提供有限的I/O地址访问权限·Windows限制应用程序访问I/O地址

查询输出通达信c+通达信c+接口,接口,通达信c+接口,接口

中断传送

中断标志·IF=处理器开中断可以响应,允许中断,中断开放·IF=0,处理器关中断不能响应,禁止中断,中断被屏蔽·关中断的情况系统复位后任何一个中断被响应后执行关中断指令CLI后·开中断的方法执行开中断指令STI执行中断返回指令IRET恢复中断前IF状态

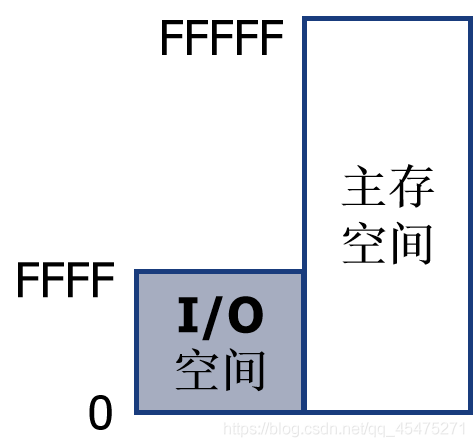

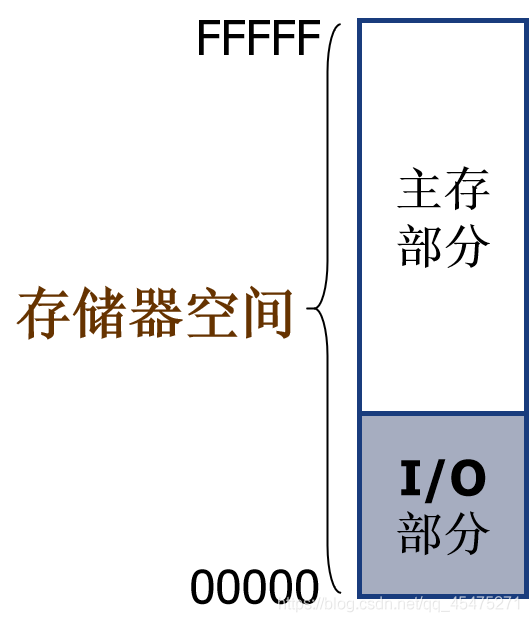

I/O端口的编址

·实现外设与主机的数据传送使I/O通达信c+通达信c+接口,接口,通达信c+接口,接口的主要功能之·计算机主机有多种与外设传送数据的方式·通过处理器执行I/O指令完成无条件传送、查询传送、中断传送·以硬件为主,加快传输速度直接存储器存取、使用专门的I/O处理机

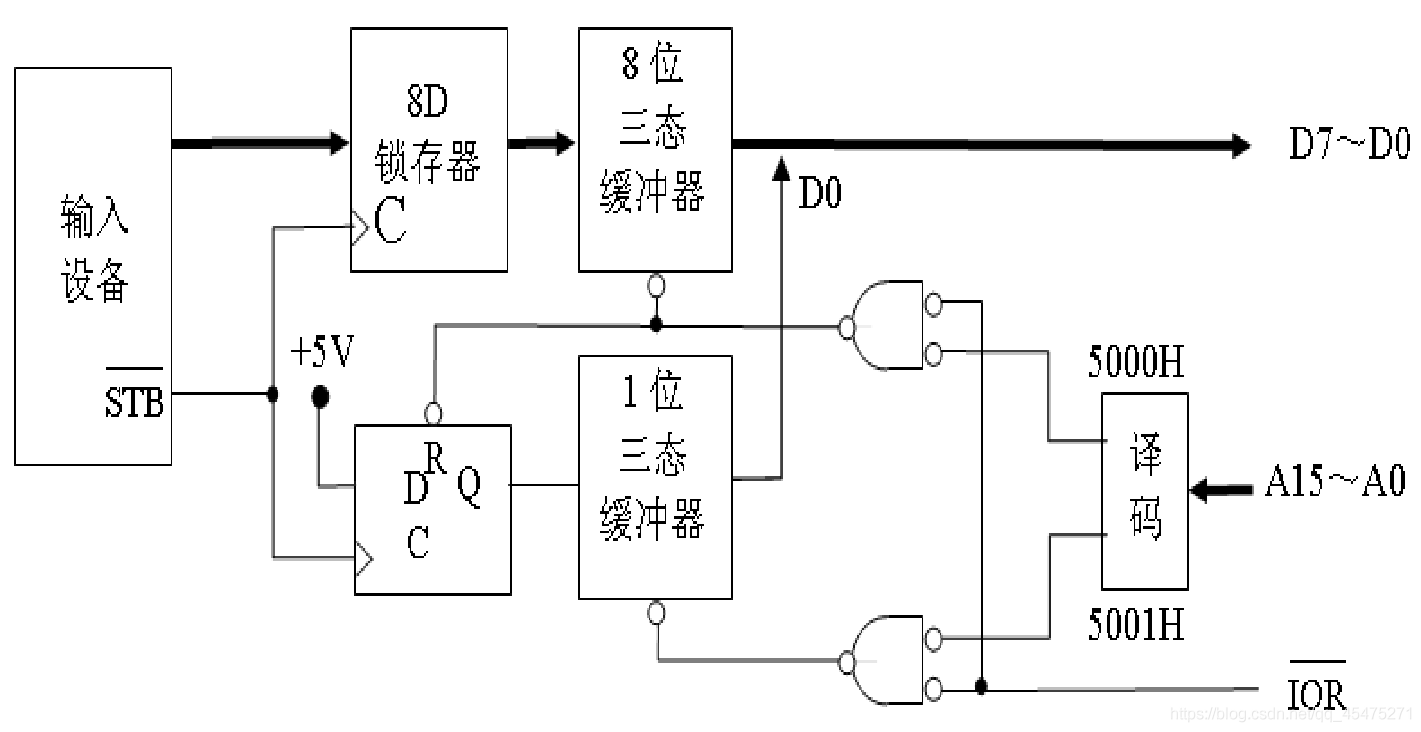

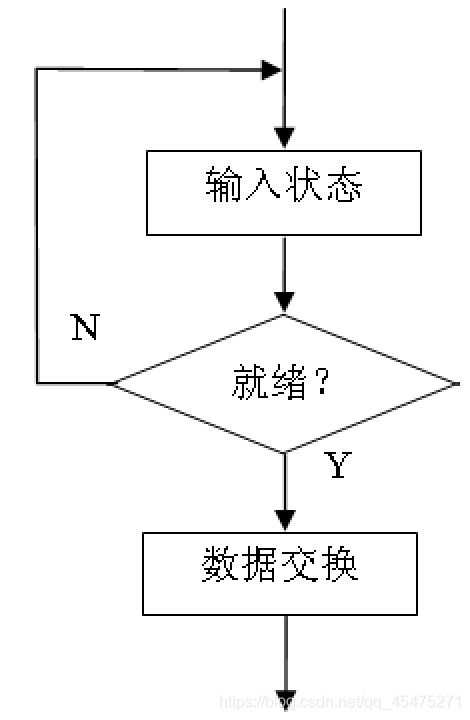

查询传送有查询和传送两个环节首先查询外设工作状态,检测、等待外设准备就绪,进行数据传输

中断控制系统

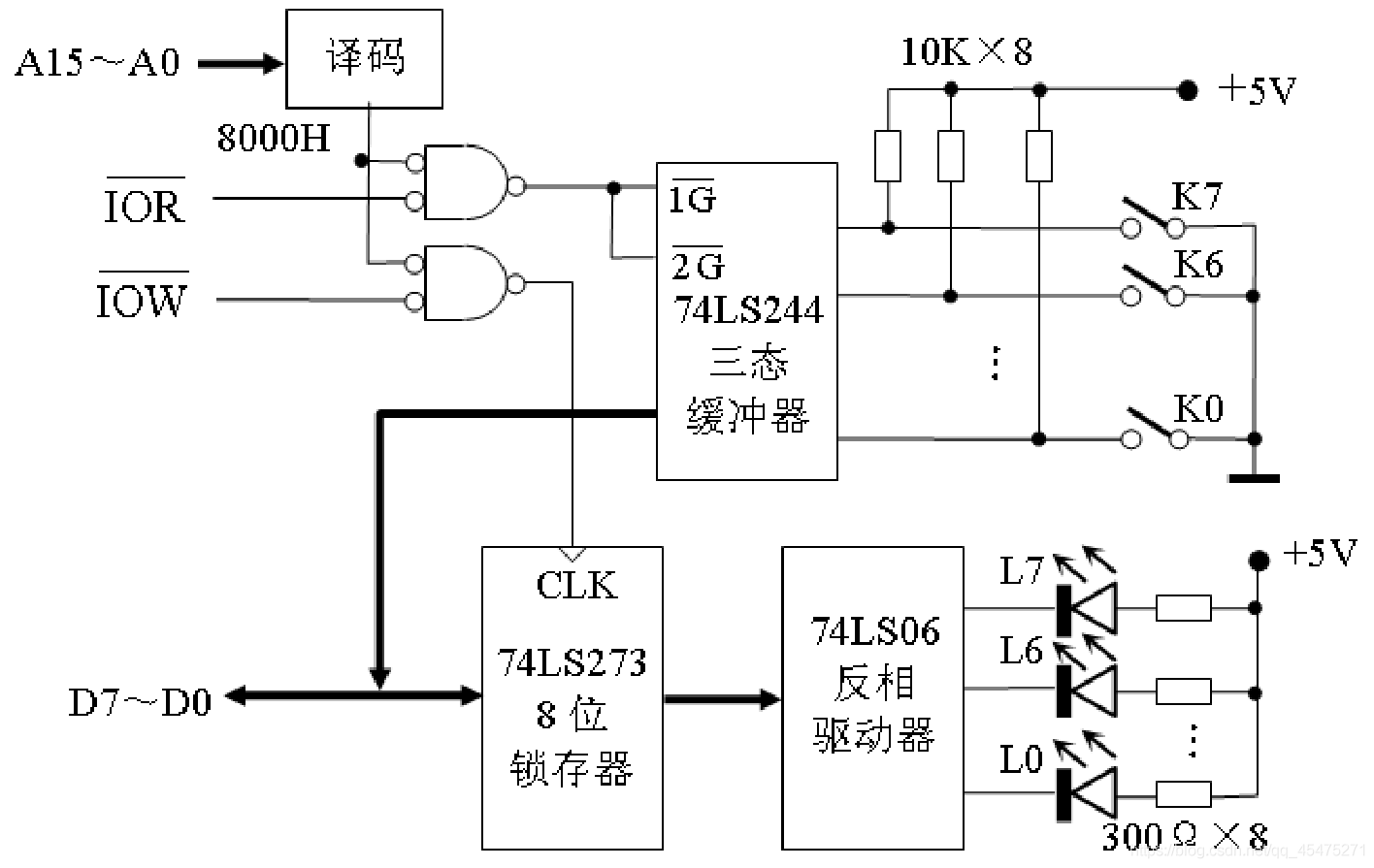

无条件传送通达信c+通达信c+接口,接口,通达信c+接口,接口·三态缓冲器74LS244构成输入端口,其两个控制端被连接在一起,连接8个开关K7~K0,开关的输入端通过电阻挂到高电平上,另一端接地。开关打开,缓冲器输入端为开关闭合,缓冲器输入端为0。·8位三态缓冲器构成数据输入寄存器,假设I/O地址被译码为8000H,以DX=8000H为I/O地址,执行INAL,DX输入指令就形成I/O度总线周期,产生读控制IOR信号低有效。译码输出与读控制同时低有效,使得三态缓冲器控制端低有效。开关的当前状态被三态缓冲器传输到数据总线D7~D0上,此时处理器恰好读取数据总线的数据,开关状态被送到了AL寄存器:其中某位Di=0,说明开关Ki闭合;Di=1说明开关Ki断开。不以8000H为地址/不执行IN指令,三态缓冲器的控制端就无效,相当于与数据总线断开。·8位锁存器74LS273构成输出端口,当CLK出现上升沿时锁存数据,被锁存的数据输出,经反相驱动器74LS06驱动8个发光二极管L7~L0发光。74LS06每个输出线经过电阻挂到高电平上。当处理器某个数据总线Di输出1经反相为0接到发光二极管Li负极,发光二极管Li正极接高电平,形成导通电流,Li点亮。·8为锁存器就是数据输出寄存器,假设经译码其I/O地址为8000H。以DX=8000H为I/O地址,执行OUTDX,AL输出指令就形成I/O写总线周期,产生IOW信号低有效。译码输出与写控制同时低有效,使得8位锁存器CLK为低,经过一个时钟周期,译码输出或写控制无效将使得CLK恢复为高。在CLK上升沿,8位锁存器将锁存器此时出现在其输入端D7~D0的数据,而此时处理器输出的正是AL寄存器的内容。

;读取8个开关状态,当开关闭合LED亮,并调用延时子程序DELAY保持一段时间

MOV DX,8000H ;DX指向输入端口

IN AL,DX ;从输入端口读开关状态

NOT AL ;求反

OUT DX,AL ;送输出端口显示

CALL DELAY ; 调子程序DELAY进行延时

无条件传送和查询传送/同步传送

采用向量中断机制能够处理256个中断用中断向量号0~255区别可屏蔽中断需要中断控制器实现优先权管理

I/O端口与存储器地址独立编址·I/O端口单独编排地址,独立于存储器地址·用M/IO区分,有IN/OUT、MOV指令·优点:I/O端口的地址空间独立控制和地址译码电路相对简单专门的I/O指令使程序清晰易读·缺点:I/O指令没有存储器指令丰富I/O端口与存储器地址统一编址·将I/O端口与存储器地址统一编排·全部都用MOV指令,靠地址范围区分·优点:不需要专门的I/O指令I/O数据存取灵活·缺点:占去部分存储器空间程序不易阅读I/O地址译码与存储器地址译码在原理和方法上完全相同I/O地址不太强调连续,多采用部分译码

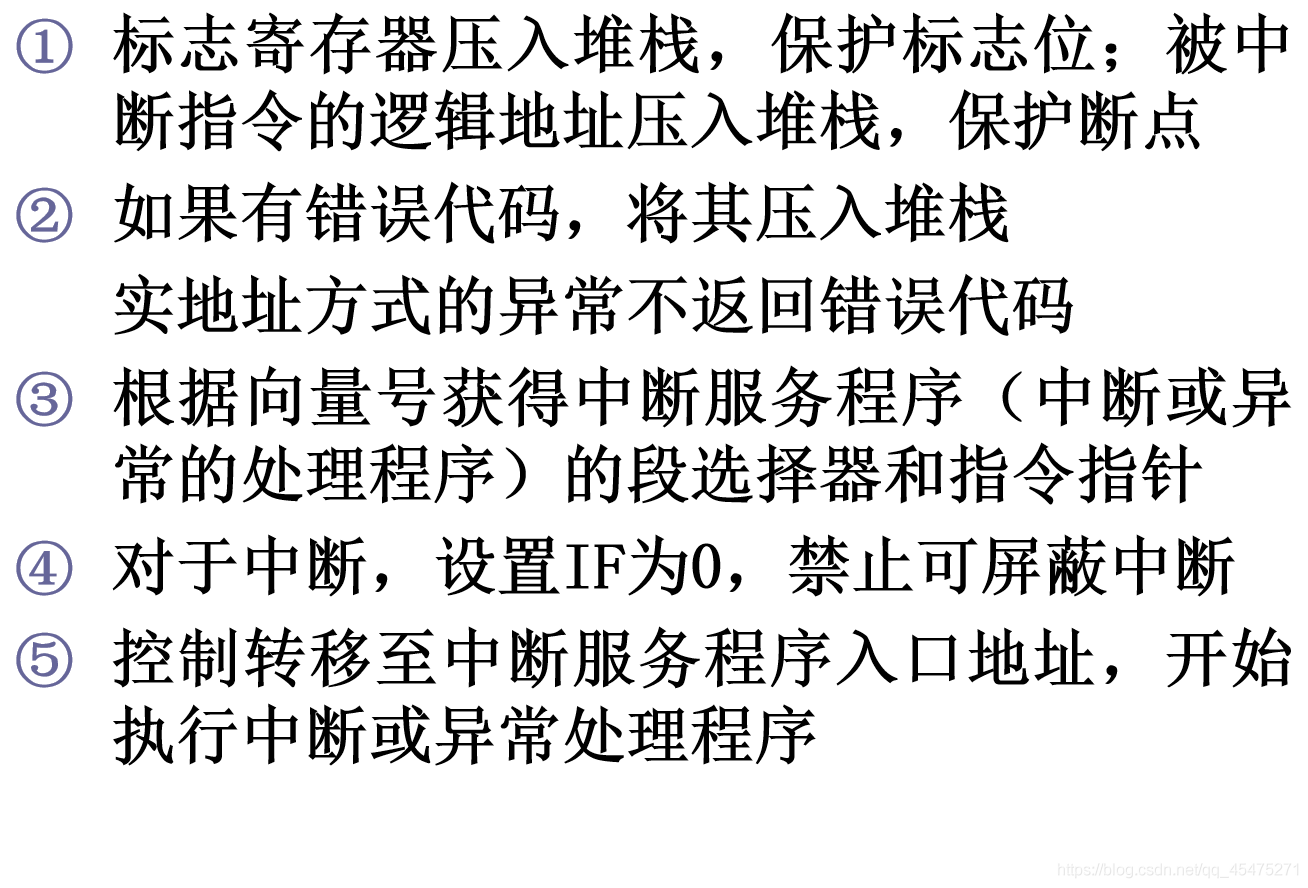

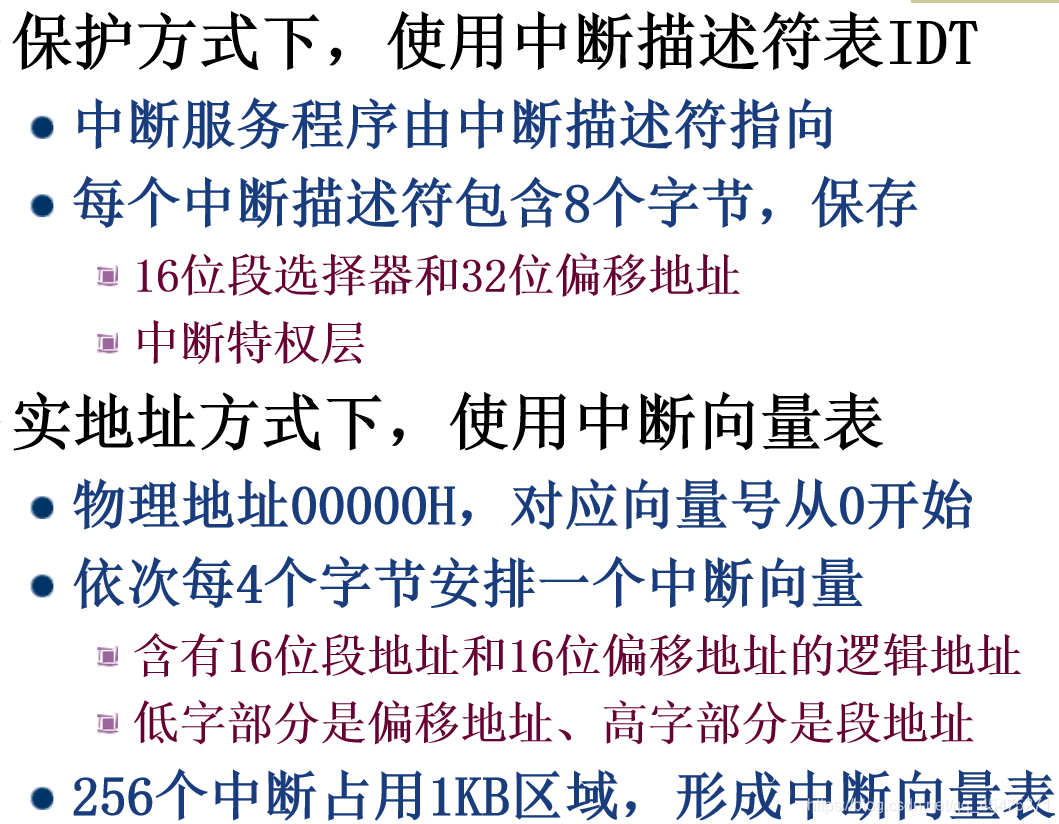

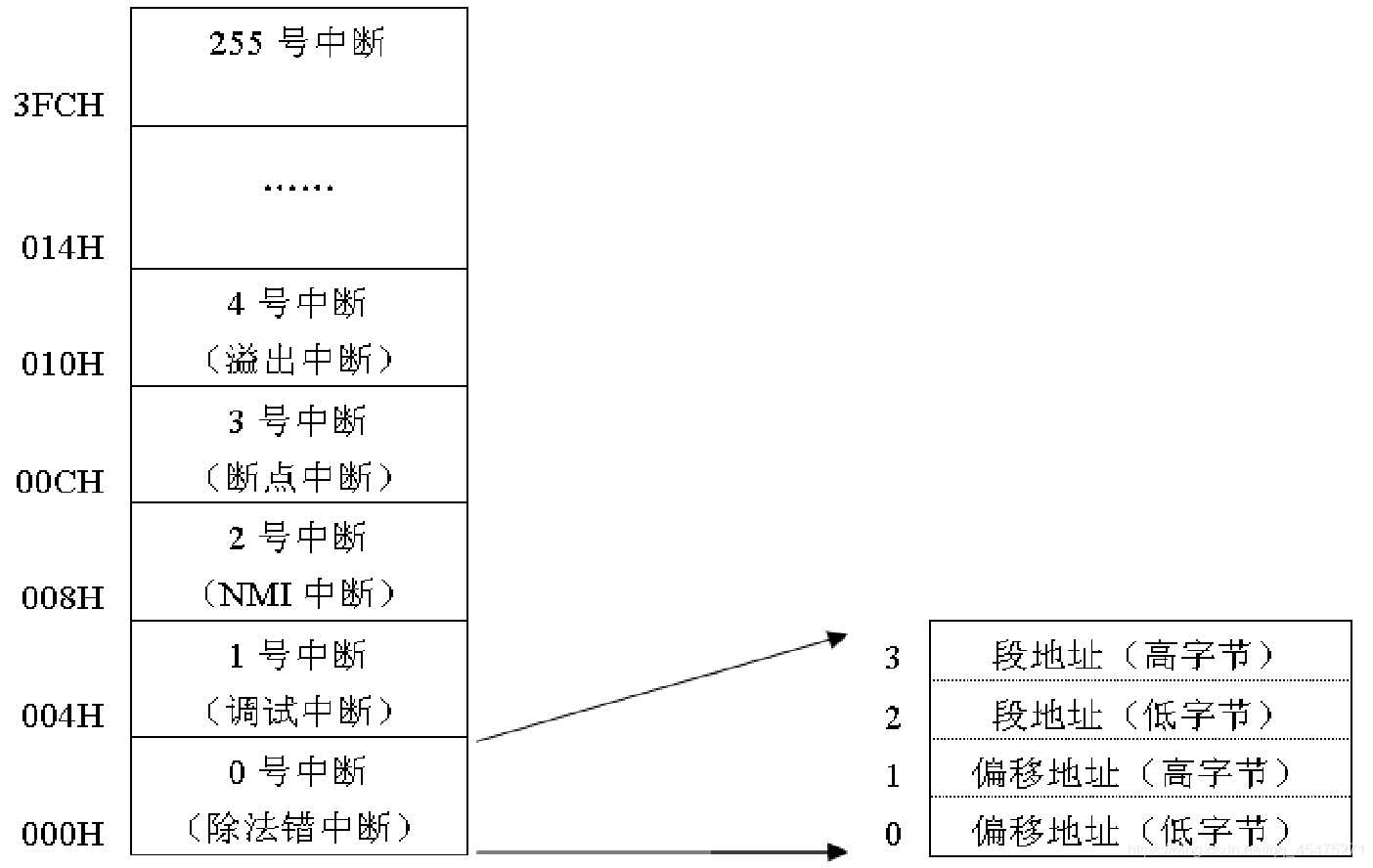

中断和异常的响应过程中断描述符表和中断向量表中断服务程序的地址含有16位段基地址CS(高字部分)和16位偏移地址IP(低字部分),共4字节,按“低对低高对高”的小端存储方法保存在中断向量表中。向量号为N的中断服务程序地址要从物理地址=N*4取得。

无条件传送

查询传送/异步传送

输入输出指令

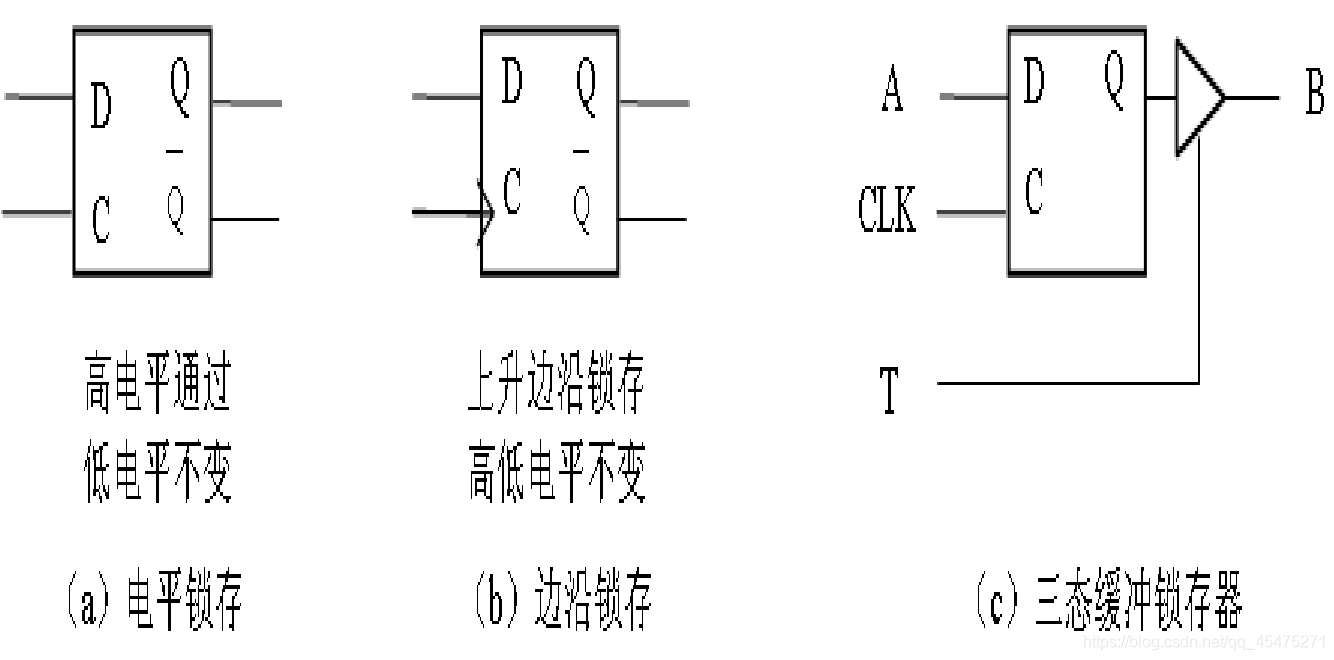

锁存器·使用D触发器构成:输入端为D端,控制端为C端;两个相反的输出信号Q和Q*;复位R或置位S控制端·电平锁存:电平控制输出能跟随输入变化·边沿锁存:输出只能锁存输入的状态74LS27上升沿锁存的8位边沿锁存器74LS37电平锁存的8位三态缓冲锁存器74LS37边沿锁存的8位三态缓冲锁存器通达信c+通达信c+接口,接口,通达信c+接口,接口电路·输入通达信c+通达信c+接口,接口,通达信c+接口,接口电路连接开关:读取开关状态·输出通达信c+通达信c+接口,接口,通达信c+接口,接口电路连接发光二极管LED·功能要求:开关闭合时,将相应LED点亮·调用延时子程序DELAY保持一定时间

mov dx,8000h ;DX指向输入端口

in al,dx ;从输入端口读开关状态

not al ;求反

out dx,al ;送输出端口显示

call delay ;调子程序DELAY进行延时

查询过程·设计实现查询功能的电路连接外设的状态输入信号保存在状态寄存器中通过状态端口读取·外设的工作状态在状态寄存器中使用一位或若干位表达,查询通过输入指令来实现·有多个状态,按照一定原则轮流查询,先检测到就绪的外设先开始数据传送·实际中常引入超时判断·查询传送工作可靠,具有较广的适用性·查询需大量时间,效率较低查询输入通达信c+通达信c+接口,接口,通达信c+接口,接口读取状态端口查询外设状态,若已就绪,读取数据端口得到外设提供的数据

mov dx,5001h ;DX指向状态端口

status: in al,dx ;读状态端口

test al,01h ;测试状态位D0

jz status ;D0=0,未就绪,继续查询

dec dx ;D0=1,就绪,DX改指数据端口 inc是加一dec是减一

in al,dx ;从数据端口输入数据

·中断是微机系统中非常重要的一种技术·利用外部中断微机系统可以实时响应外部设备的数据传送请求、能够及时处理外部意外或紧急事件·利用内部中断处理器为用户提供了发现、调试并解决程序执行时异常情况的有效途径

三态缓冲器

处理器与慢速变化的设备交换数据外设总是处于“就绪”状态,随时可以进行数据传送无条件传送的通达信c+通达信c+接口,接口,通达信c+接口,接口电路:只考虑数据缓冲

内部中断内部中断是由于处理器内部执行程序出现异常引起的程序中断除法错异常调试异常断点异常溢出异常无效代码异常通用保护异常页面失效异常……

I/O通达信c+通达信c+接口,接口,通达信c+接口,接口的典型结构

中断工作过程中断源的识别·向量中断在中断响应周期,处理器获得中断向量号一个中断向量号对应一个中断自动转向相应的中断服务程序·中断查询中断请求保存在中断状态寄存器处理器依次查询中断状态寄存器某个中断请求状态有效说明其提出请求转向对应的中断服务程序中断优先权排队·中断优先权每个中断源被处理的级别·中断优先权排队事先为每个中断源所确定的优先处理顺序·查询中断时依次查询,先查询的中断具有较高的优先权·硬件电路实现时分布方式的菊花链排队电路集中方式的编码电路和比较电路

文章为作者独立观点,不代表股票交易接口观点