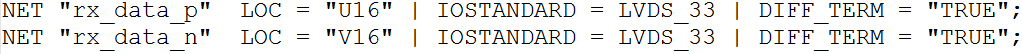

差分信号输入端需要端接匹配电阻,如果输入端为FPGA管脚,可以通过配置,使能其内置端接电阻,阻值默认为100Ω。UCF配置LVDS通达信股市行情接口控件,接口如下:

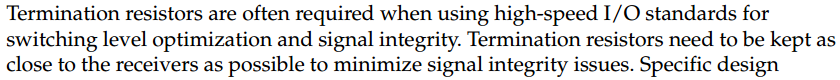

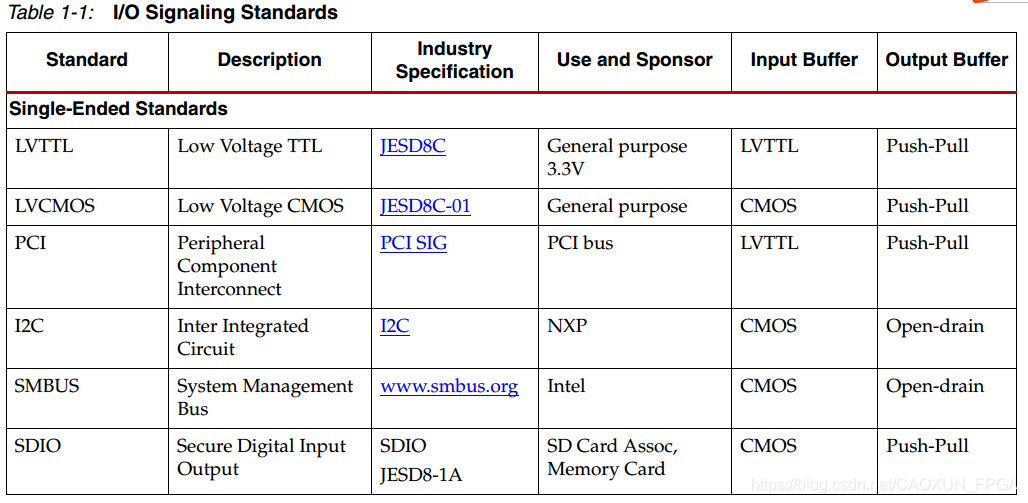

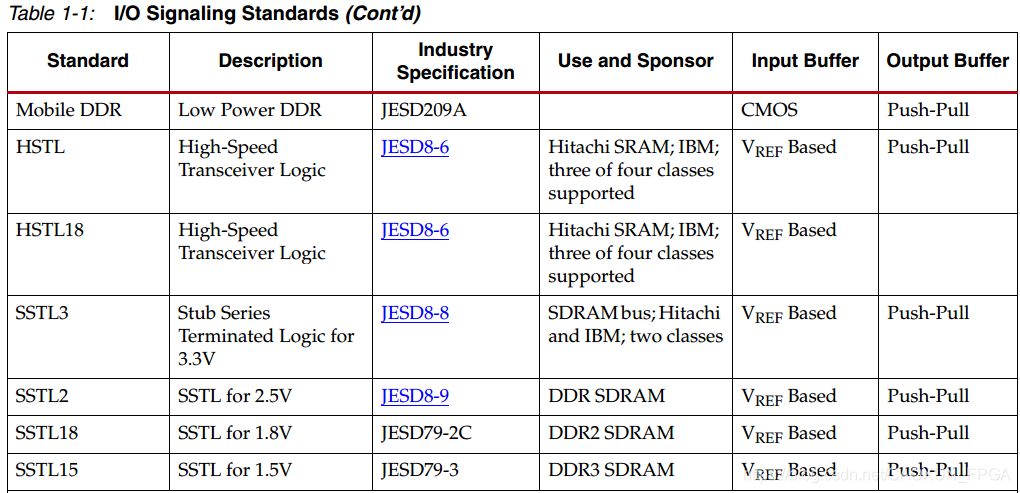

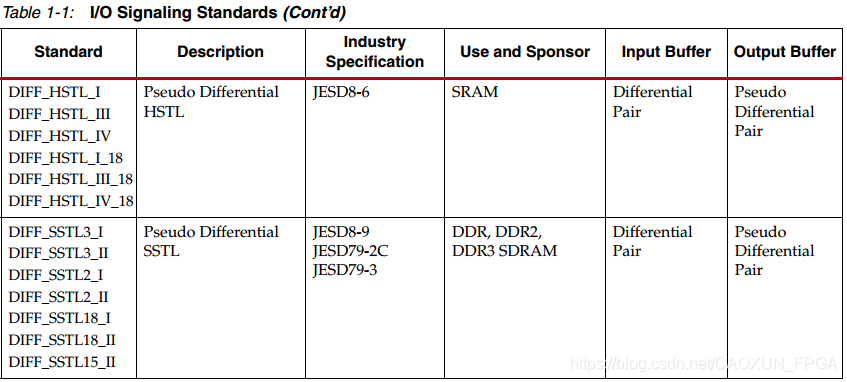

由上可知,一些单端IO通达信股市行情接口控件,接口也需要输入端接电阻来匹配信号的完整性,例如HSTL,SSTL。SSTL电平通常应用在DDRSRAM中,例如SSTL18应用在DDRSSTL15_II应用在DDR3中。详见下所示。

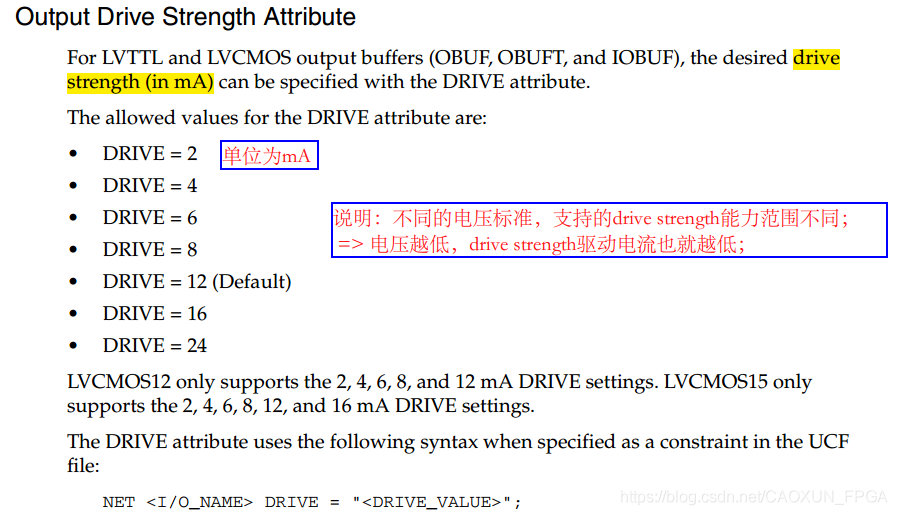

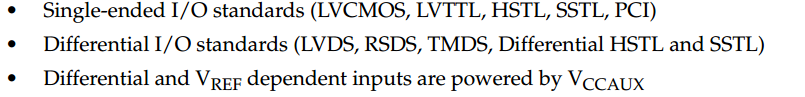

常见IO通达信股市行情接口控件,接口属性包括:电平标准,输出压摆率,输出驱动能力,上/下拉。详细设置参考下文。

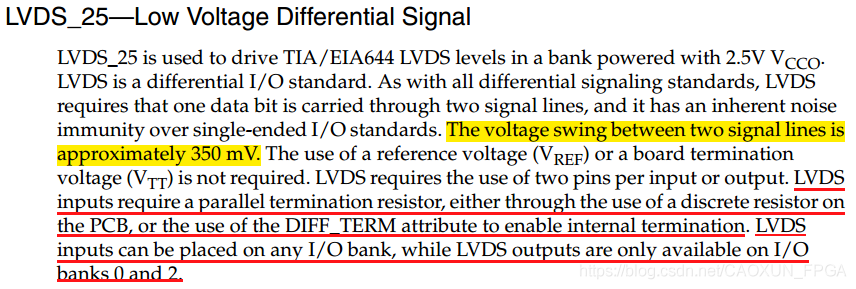

LVDS差分IO通达信股市行情接口控件,接口驱动

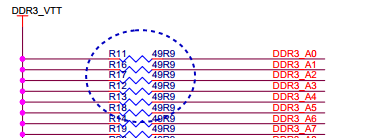

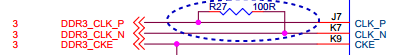

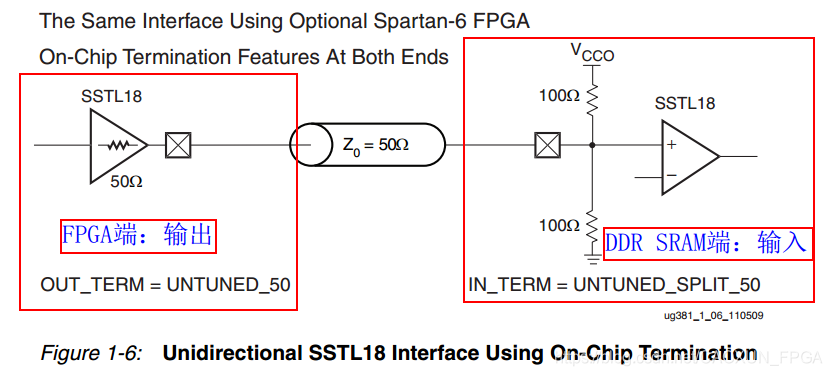

地址总线输入端需匹配50Ω端接电阻,差分时钟输入端需要匹配100Ω的端接电阻,见下所示。

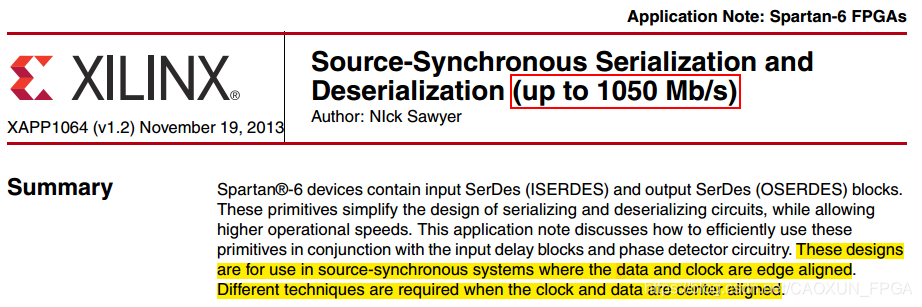

最近准备采用XilinxFPGA进行多机通信,即主FPGA芯片将采集到的不同层的像数据流分别输出给对应的4块从FPGA芯片中,主从FPGA之间的连接机制采用星形拓扑结构。经计算,像数据流通达信股市行情接口控件,接口速率需要数百兆比特/秒,因此需要调研FPGA支持的常见IO通达信股市行情接口控件,接口标准,及每种通达信股市行情接口控件,接口的应用场合。现在项目使用的FPGA芯片为Spartan6系列,故参考的userguide为UG38《Spartan-6FPGASelectIOResources》。

差分输入端接电阻

每一组bank均有独立的Vcco和Vref,便于配置variableIOstandard;

FPGA驱动DDR3SRAM芯片时,FPGA作为输出源端,SRAM芯片作为终端,故FPGA需要配置outputdriver的相关属性参数attributes。SRAM作为inputreceiver,需要进行端接电阻匹配,由于没有内置片上端接电阻,故需要在SRAM输入管脚外接匹配电阻,由于数据端口是双向端口,故输入端是高阻状态,无需匹配。而地址总线通达信股市行情接口控件,接口和差分时钟输入通达信股市行情接口控件,接口需要匹配对应阻值的电阻。

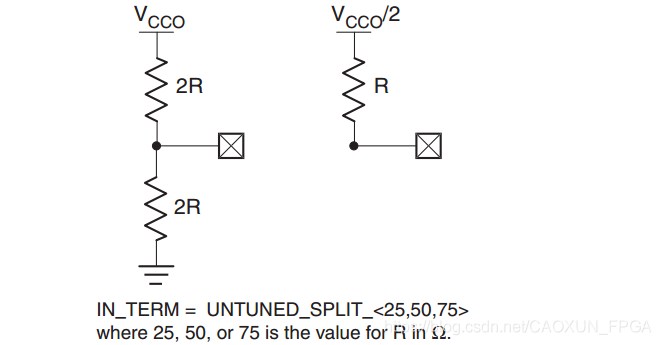

单端输入端接电阻

为减少SSO的大量输出管脚电平同一方向切换的干扰,可以增加virtual

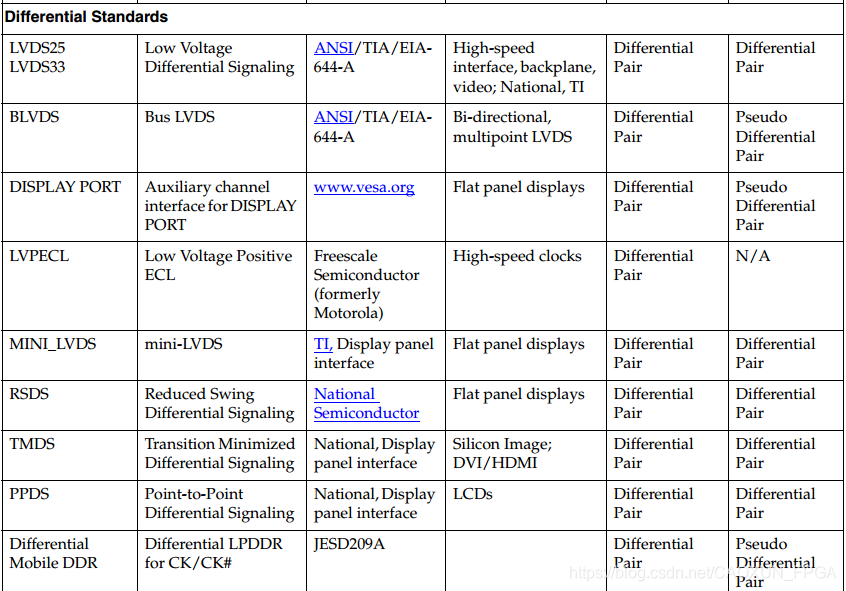

LVDS:低压差差分信号,每位数据需要一对差分信号线,相较于单端通达信股市行情接口控件,接口,差分通达信股市行情接口控件,接口可以抑制共模噪声,电压摆幅约350mV,因此信号传输功耗较低。LVDS通达信股市行情接口控件,接口传输速率上限可达125Gbit/s,如果配合相应的编码规则和使用SERDES技术,可以保证常用高速信号通信。

高速IO通达信股市行情接口控件,接口应用举例

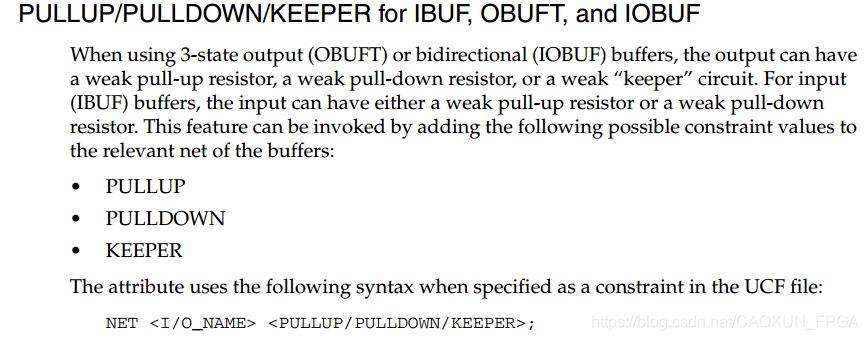

通过UCF文件进行约束,是否使用单端输入端接电阻,语法规则如下:

第二种:采用LVDS33/25通达信股市行情接口控件,接口标准,应用于IOSERDES的高速串行通信,属于differentialIOstandard;

说明:SRAM输入管脚的端接电阻尽可能靠近管脚,以保证信号的完整性;

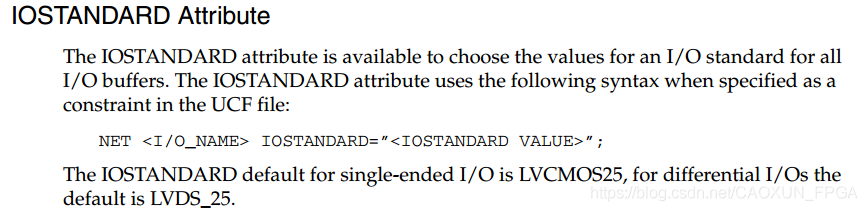

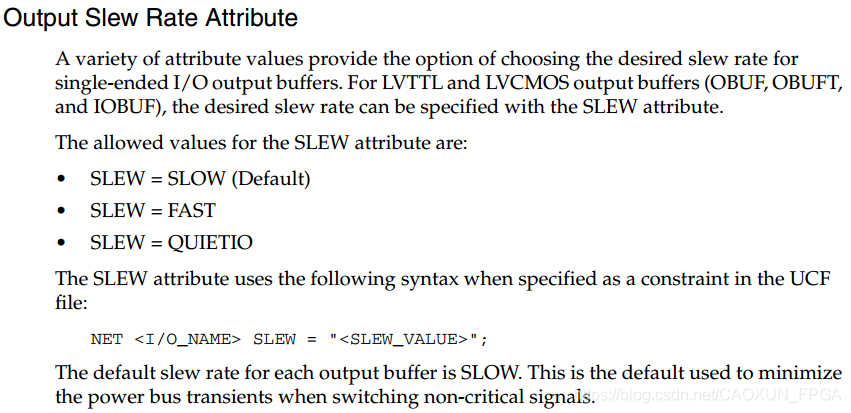

设置IO通达信股市行情接口控件,接口属性

XilinxFPGA芯片不同的Bank支持的IO通达信股市行情接口控件,接口标准范围略有所不同,但是同一Bank必须使用同一outputdrivevoltage(VCCO)。

DDR3SRAM通达信股市行情接口控件,接口驱动

第一种:采用SSTL15_II通达信股市行情接口控件,接口标准,应用于DDR3SRAM,属于single-endIOstandard;

SRAM输入端IOstandard,地址管脚和数据管脚尽可能均匀分配在某一个或多个Bank中。

VCC/GNDpins,即将该bank未用到的管脚在FPGA程序中设置为GND或VCC;

常见IO通达信股市行情接口控件,接口可分为单端IO通达信股市行情接口控件,接口和差分IO通达信股市行情接口控件,接口,详细的IO标准参见下单端IO通达信股市行情接口控件,接口和差分IO通达信股市行情接口控件,接口均满足高速通达信股市行情接口控件,接口传输,区别在于应用场合不同。

压摆率和上下拉采用默认参数,SLOWslewrate,12mAoutputdrive。

FPGA输出端IOStandard在UCF文件中参数配置如下:

地址总线输入通达信股市行情接口控件,接口差分时钟输入通达信股市行情接口控件,接口

端接电阻

说明:由上可知,FPGA作为输出端,其端接电阻可以通过内置端接电阻配置完成,但如果DDRSRAM作为后一级的输入端,该芯片没有片上端接电阻,故需要外接50Ω的输入匹配电阻。

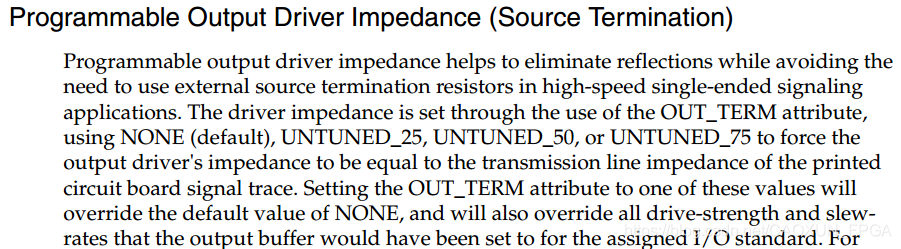

由上可知,输出端也可以配置输出端接电阻,以减少信号的反射,应用在高速单端信号场合,例如FPGA输出驱动DDR3芯片。输出端接电阻也是optional可选项,常见阻值R为none,25Ω,50Ω,75Ω。通过UCF文件进行约束,是否使用单端输出端接电阻,语法规则如下:

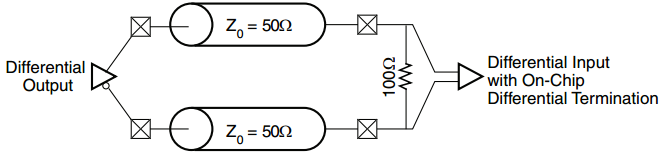

通常需要在差分输入端并行端接100Ω的电阻,FPGA在差分输入接收器提前内置了端接电阻,其阻值R为100Ω,为可选项optional。设计者也可以采用外接端接电阻来进行电阻匹配,阻值选择更灵活。采用片上内置的端接电阻可以节省无聊和缩小PCB面积。

输出端接电阻

0引言

Spartan6FPGA所有Bank均支持LVDS差分输入,但只有Bank0和Bank2支持LVDS差分输出;

XilinxFPGA提供和支持高性能、可配置、多样化的通达信股市行情接口控件,接口标准。主要的可配置属性为On-chiptermination,outputstrength,slewrate等。

通过UCF文件进行约束,是否使用差分输入端接电阻,语法规则如下:NETDIFF_TERM='

基于FPGA的高速IO通达信股市行情接口控件,接口应用的常见例子有两种,详见下文。

常见IO通达信股市行情接口控件,接口标准

由上2可知,当使用高速IO通达信股市行情接口控件,接口时,在接收端通常需要匹配的端接电阻,有利于高低电平的转换和提高信号的完整性,且端接电阻尽可能的放置在接收端。

当今大厂家会基于其IO通达信股市行情接口控件,接口的总线应用场合提出新的IO通达信股市行情接口控件,接口标准,随后被其他厂家所使用。每一种IO通达信股市行情接口控件,接口标准均有其特有的电压、电流、输入输出缓冲和端接匹配技术要求。XilinxUserGuide详细列出了常见的各种IO通达信股市行情接口控件,接口的种类,定义及应用场合,详见下文。

常见IO通达信股市行情接口控件,接口标准&应用

文章为作者独立观点,不代表股票交易接口观点